Lam Research | 用钼混合金属化突破铜的瓶颈

专属客服号

微信订阅号

大数据治理

全面提升数据价值

赋能业务提质增效

正文共:2843 字;预计阅读时间:8 分钟

编译自:

Breaking the Copper Bottleneck With Molybdenum Hybrid Metallization-Tae Yeon Oh, Lam.

在先进半导体逻辑器件中,缩小后端工艺(BEOL)的尺寸是一项重大挑战。后端工艺中的金属线和接触孔填充历来使用铜作为电导体。但随着器件尺寸的缩小,铜的使用变得成了问题。最新后端工艺结构中铜金属线和通孔的小临界尺寸(CD)导致电阻增加,影响了器件性能。

这种电阻的增加源于小体积铜的电阻率升高。1

由于可靠性问题,铜双大马士革(dual damascene,DD)工艺在低于特定阻挡层金属厚度的缩放方面受到限制。2

应力诱发空洞(SIVs)也会导致互连线电阻增加。3

混合金属化

混合金属化是一种新技术,它采用自下而上的沉积方法,用无阻挡层金属(barrierless metals)预先填充通孔。无阻挡层金属是指在金属与周围的电介质或半导体材料之间不需要单独扩散阻挡层的金属互连。这种混合金属化技术之后会进行传统的铜双大马士革工艺。

这种技术最初可应用于底部通孔接触区域,由于器件尺寸更小,这些区域的通孔电阻正迅速增加,该技术有望用替代性无阻挡层金属替代所有铜线路和通孔。

Lam 开展了一项路径探索研究,将传统的铜双大马士革方案与采用钼(Mo)的混合金属化方案进行了比较。Lam 的研究使用了 SEMulator3D®,该工具还被用于制定工艺规范,以获得最佳的通孔金属线轮廓。

图 1 展示了不同金属通孔方案的通孔/线路电阻图表。在这个例子中,与传统的铜双大马士革工艺方案相比,钼混合方案的总电阻优势约为55%。

图1:不同金属/通孔方案的 M1 至 M3 电阻(孔/线路)

选择性阻挡层沉积(Selective barrier deposition,SBD)技术也可用于避免在通孔顶部沉积阻挡层金属。使用 SBD 可使总电阻额外降低15%(图 1 中的右侧数据集),而通孔电阻在有无 SBD 的情况下几乎相同。

如图 2 所示,正如预期的那样,同时使用钼通孔和 SBD 技术的总电流密度要高得多,因为它们表现出更低的电阻值。

图2:各种金属/通孔方案的电流密度。红色和绿色区域表示较高的电流密度

优化金属化

Lam 使用传统的铜双大马士革和钼混合方案研究了应力分布。与使用钼通孔方案相比,使用铜双大马士革方案时,M1 和 V1 之间在 Z 方向上的应力差距更大。这在通孔 V1 和阻挡金属层之间最为明显(见下图中的红色区域)。

铜的 V1 与 M1/M2 之间的最大应力差更大。由于应力梯度,金属/阻挡层界面或金属/电介质界面可能会产生应力诱导的空洞。4 使用铜双大马士革工艺形成的通孔底部出现空洞的概率高于使用钼混合金属化工艺形成的通孔。

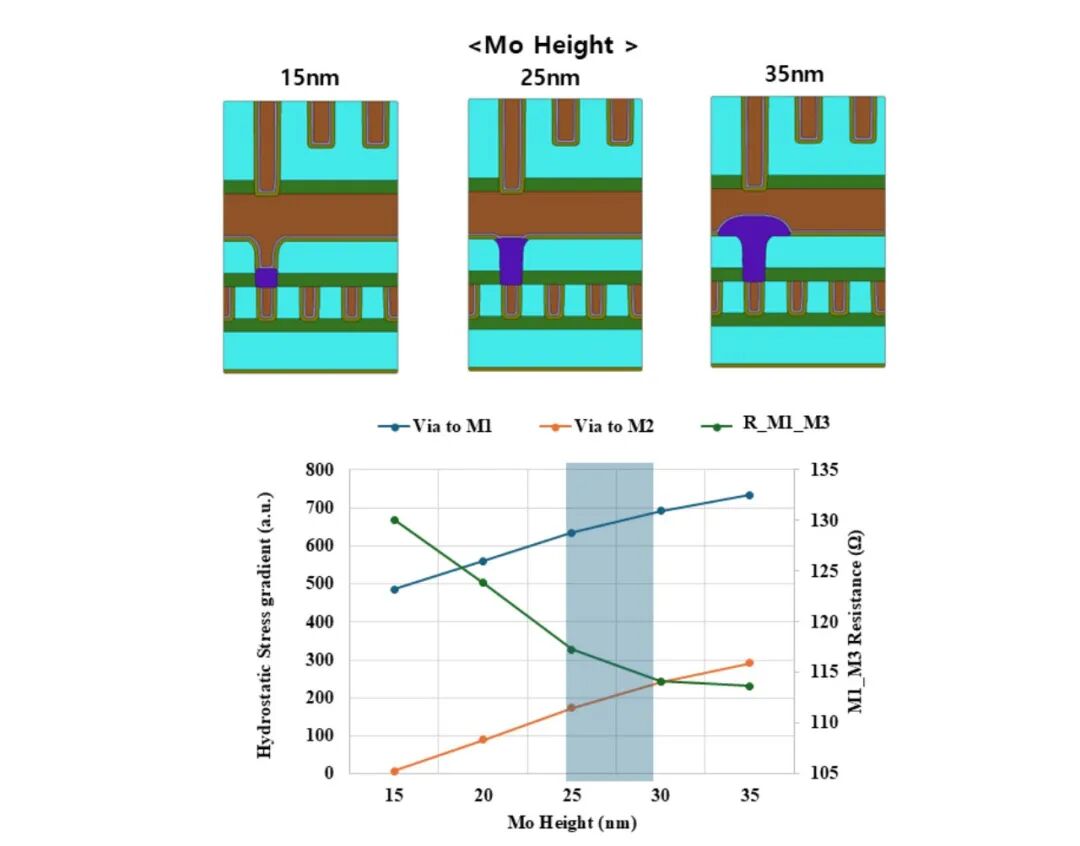

图4:通孔电阻和静水应力与钼高度的函数关系。

在 M1 至 M3 后端互连方案中,分析了钼预填充轮廓内的电阻和机械应力。钼通孔与 M1 之间以及钼通孔与 M2 之间的静水应力(hydrostatic stress)梯度随着钼高度的增加而增大。M1 至 M3 的总电阻随着钼高度的增加而减小。

由于当钼(Mo)高度超过 25 nm 时,电阻斜率会趋于饱和,且随着钼高度的增加,铜/阻挡金属与钼之间的 M1 应力梯度会增大,因此最佳的钼高度可能是填充至通孔高度并满足电阻和应力目标所需的量。

通孔应力也可以通过使用具有不同特性(如本征应力和工艺温度)的材料来控制。下图显示了钼通孔应力与钼本征应力的函数关系。通过选择具有压缩本征应力的钼材料,可以降低通孔的静水应力。

如下图所示,通孔的应力随温度升高而降低;然而,M2 应力却迅速增加。由于应力梯度较高可能会导致应力诱发空洞,在 Lam 的示例中,通过将温度保持在约 400°C,通孔和 M2 之间较小的应力值差异是更理想的。在较高温度下,M2 应力也可能从拉伸应力变为压应力。

图5:通孔具有本征应力对应的静水应力

图6:孔静水应力及其分布随工艺温度的变化。

为了利用混合金属化确定最佳的通孔金属线轮廓,Lam 在 SEMulator3D 中进行了包含 400 次实验运行的均匀蒙特卡洛模拟。通过线性回归分析,Lam 确定了四个有助于实现该轮廓的参数候选。如图 6 所示,随着通孔顶部关键尺寸(CD)和底部关键尺寸的增大,通孔应力和总电阻会减小。

图6:不同工艺参数的敏感性分析及其对静水应力、M1-M3 电阻和 M1-M2 电容的影响。所分析的参数包括通孔顶部和底部的关键尺寸、通孔高度以及 M2,其中显示了用于电容的计量目标。

相反,随着通孔高度的增加,通孔应力和总电阻也会增加。当通孔高度(即M1和M2之间的距离)减小且通孔关键尺寸(CD)增大时,M1和M2之间的电容会增加。因此,由于M1和M2之间高介电场中的泄漏电流,通孔高度的减小存在一定限制。这种泄漏电流可能会导致诸如时间相关介质击穿(TDDB)等内在的可靠性问题。

Lam通过敏感性分析得出了最佳的通孔轮廓(图 7)。

结论

在本研究中,Lam展示了一种为使用钼的混合金属化提供路径规划指导的方法。通过虚拟制造和虚拟实验设计(DOE),Lam 能够确定最佳的钼通孔轮廓,该轮廓将最大限度地减少导致空洞的机械应力,并最大限度地降低 RC 寄生效应。利用这种技术,Lam 可以预测采用混合金属化等新工艺方案时工艺变化带来的影响,而无需花费大量基于晶圆实验的时间和成本。

TY Oh 是韩国 Semiverse Solutions 研发中心的一名半导体工艺与集成工程师。

参考文献:

1 Properties of Ultrathin Molybdenum Films for Interconnect Applications, Materialia 2022, Vol. 24, p. 101511.

2 On-Chip Interconnect Trends, Challenges, and Solutions: How to Keep RC and Reliability Under Control, 2016 IEEE Symp. VLSI Technol., pp. 182–183.

3 Semidamascene Interconnects for 2nm Node and Beyond, IEEE IITC 2020, pp.4-6.

4 Simulation and Experiments of Stress Migration for Cu/Low-k BEoL, IEEE Trans. Device Mater. Reliab. 2004, Vol. 4, pp. 523-529.

↓设置星标,精彩不错过↓

↓扫一扫,总一款适合你↓

本文仅作行业信息分享、技术交流与岗位对接使用,不涉及任何涉密内容。

欢迎关注本公众号,获取更多半导体设备、工艺、产业动态与优质岗位信息。

如有疏漏、内容建议或岗位咨询,欢迎留言交流。